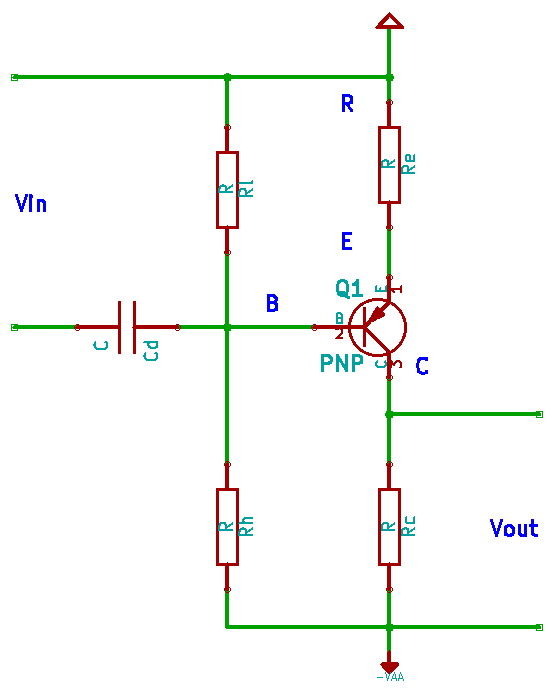

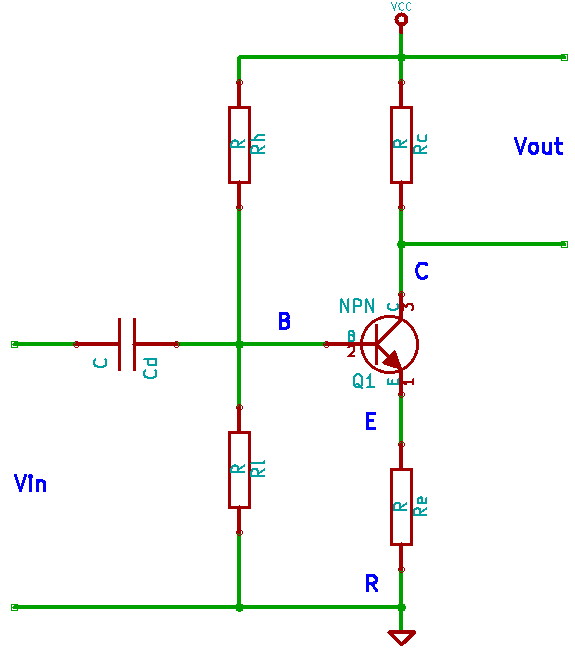

Ignorons dans un premier temps Re qui est la résistance de plus faible valeur du montage.

Rh et Rl forment un diviseur potentiométrique pour rendre Q1 passant.

Comme Q1 est passant, il y a une chute de tension sur Rc.

Pour avoir une bonne dynamique de sortie, on s'arrange pour que la polarisation provoque une chute de tension sur Rc de la moitié de la tension d'alimentation (Vcc/2).

Par exemple, si l'alimentation est de 12V, Q1 est polarisé pour amener son collecteur à 6V. Ainsi, en faisant varier le courant de base on pourra soit faire monter cette tension de 5V (6V+5V=11V < 12V) en amenant Q1 à la limite de la coupure, soit la faire descendre de 5V (6V-5V = 1V > 0V) en amenant Q1 à la limite de la saturation. Le signal alternatif sur la sortie peut ainsi être de 5V crête maximum.

Aux bornes de Re, nous retrouvons la tension d'entrée -0V7.

Re sert donc a faire varier le courant dans le transistor en fonction des variations de la tension d'entrée.

Aux bornes de Rc, nous obtenons le signal d'entrée amplifié selon le rapport des résistances Rc/Re.

Remarquons que si nous augmentons la tension d'entrée sur la base, le transistor devient plus passant et la tension de sortie descend (chute de tension plus importante sur Rc), et inversement.

Le signal de sortie est inversé par rapport au signal d'entrée, en alternatif on dit qu'il est déphasé de 180°.