ISSLg - Cours

d'électronique - Électronique (ELO)

Les transistors

bipolaires - le montage différentiel

Navigation> electronique/elo/transistors/differentiel

Principe : on polarise deux transistors

identiques reliés par leur émetteur, le signal d'entrée est

appliqué entre les deux bases et le signal de sortie est mesuré

entre les deux collecteurs. Ce montage permet de

supprimer les condensateurs de découplage d'entrée ou d'avoir une

tension d'entrée décalée par rapport au 0V (faire la différence

entre deux tensions).

Condition de fonctionnement :

Les signaux d'entrées V+ et V-

doivent être proches l'un de l'autre sinon le montage devient

non-linéaire (distorsion du signal), ils sont aussi proches de Vr (0V).

Pour des transistors au Silicium :

-25mV < V+ < 25mV

& -25mV < V- < 25mV

Le signal amplifié (Vin) est la différence des deux signaux

d'entrées (V+ et V-), c-à-d la différence de tension entre les

deux bases :

Vin = V+ - V- = Vb1r - Vb2r =

Vb1b2

Pour des transistors au Silicium : -50mV

< Vin < 50mV

Le signal de sortie est la différence de chute de tension sur les

résistances de collecteur Rc, c-à-d la différence de tension entre

les deux collecteurs :

Vout = Vc2r - Vc1r = Vc2c1.

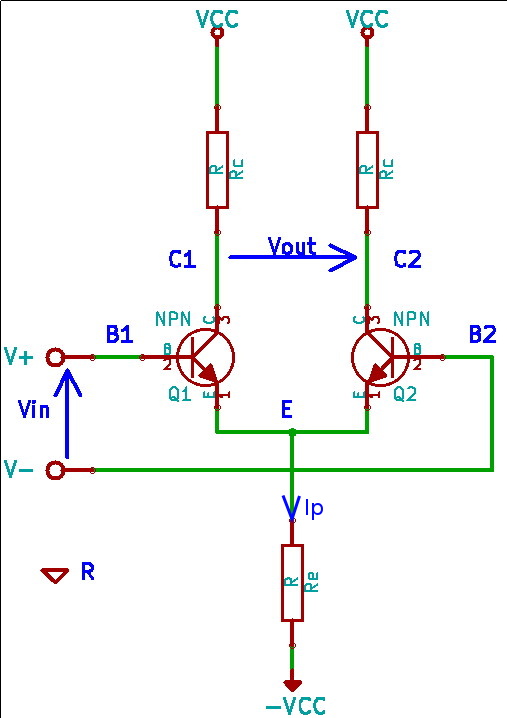

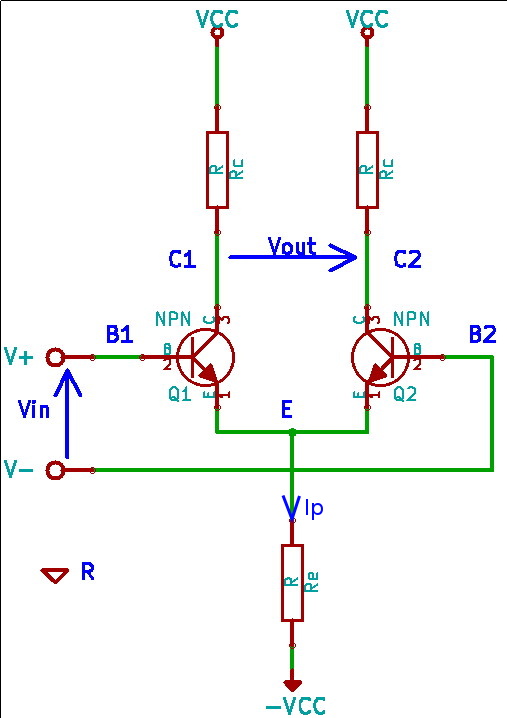

Montage

avec des NPN :

Polarisation :

Ve = -0.7V (car V+ et V- sont petits et proches de 0V).

La résistance Re est traversée par le courant de polarisation Ip :

Ip = (Vcc - 0.7V) / Re

Si Vin=0V, les transistors se partagent entre eux ce courant :

Ic = Ip / 2 = Ic1 = Ic2

Remarquons qu'un courant de base des transistors (bias current)

est nécessaire pour leur polarisation :

Iin = Ic / β

Comme les courants de collecteur sont identiques, les chutes de

tension sur les résistances de collecteur sont identiques :

Vout = Vcc - Rc*Ic2 - Vcc -

Rc*Ic1 = Rc (Ic2 - Ic1) = 0V

En petits signaux :

Impédance des transistors

(Silicium) : Ze = 0.025V / Ic

vo = Rc*ic2 - Rc*ic1 = Rc *

(+(vi/2) / Ze) - Rc * ( -(vi/2) / Ze) = Rc * (vi / Ze)

Caractéristiques :

Gain en tension : Av = Rc /

Ze

Impédance d'entrée : Zin = β

* Ze

fmin=0Hz

fmax = 1 / (2 * pi * Rx * Cbc)

où

Rx est la plus grande résistance : soit Rc, soit la

résistance interne du générateur de signaux connecté aux

entrées multipliée par Av

où Cbc est la capacité entre base et

collecteur (jonction BC=2pF typiquement)

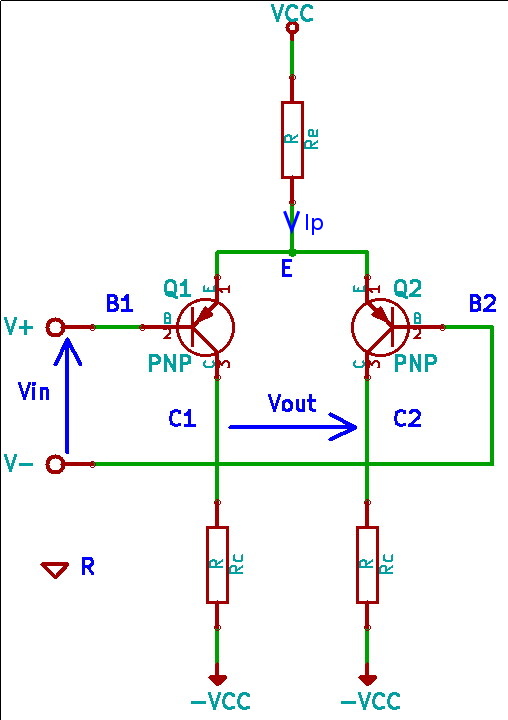

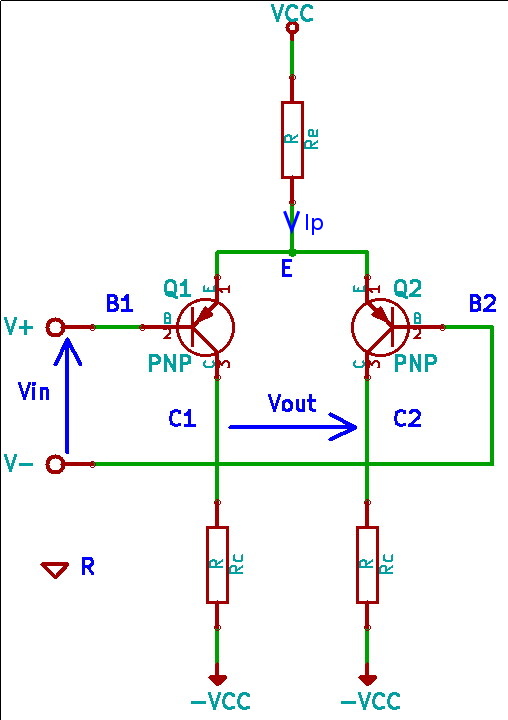

Montage

avec des PNP :

Polarisation :

Ve = 0.7V (car V+ et V- sont petits et proches de 0V).

La résistance Re est traversée par le courant de polarisation Ip :

Ip = (Vcc - 0.7V) / Re

Si Vin=0V, les transistors se partagent entre eux ce courant :

Ic = Ip / 2 = Ic1 = Ic2

Remarquons qu'un courant de base des transistors (bias current)

est nécessaire pour leur polarisation :

Iin = Ic / β

Comme les courants de collecteur sont identiques, les chutes de

tension sur les résistances de collecteur sont identiques :

Vout = -Vcc + Rc*Ic2 - (-Vcc

+ Rc*Ic1) = Rc (Ic2 - Ic1) = 0V

En petits signaux :

Impédance des transistors

(Silicium) : Ze = 0.025V / Ic

vo = Rc*ic2 - Rc*ic1 = Rc *

(+(vi/2) / Ze) - Rc * ( -(vi/2) / Ze) = Rc * (vi / Ze)

Caractéristiques :

Gain en tension : Av = Rc /

Ze

Impédance d'entrée : Zin = β

* Ze

fmin=0Hz

fmax = 1 / (2 * pi * Rx * Cbc)

où Rx est la plus grande résistance : soit Rc, soit

la résistance interne du générateur de signaux connecté

aux entrées multipliée par Av

où Cbc est la capacité entre base et

collecteur (jonction BC=2pF typiquement)

Limitation

du montage :

Pour avoir une bonne dynamique

de sortie, la résistance maximale de collecteur est Rc = Re, comme

cela les deux collecteurs se trouvent à Vcc/2 au repos.

On a alors approximativement (en négligeant les 0.7V de Vbe) :

Ip = Vcc / Rc

Ic = Ip / 2 = Vcc / (2 * Rc)

Ze = 0.025V / Ic = 0.05V *

Rc / Vcc

Av = Rc / Ze = Vcc / 0.05V

Le gain maximum dépend de la tension d'alimentation du montage,

par exemple si Vcc=5V (alimentation +5V 0V -5V) alors le gain

maximum que l'on peut espérer est de Av=100.

La tension de mode commun est la tension moyenne des tensions

d'entrées :

Vcom = ( (V+) + (V-) ) / 2

On a considéré ci-dessus que cette tension était de Vcom = 0V.

Si elle est différente, la polarisation et le gain du montage

change :

Ip = Vcc + Vcom - 0.7V => Ic change

=> Ze change =>

Zin & Av change

Amélioration

du montage :

Pour

améliorer le mode commun, la résistance de polarisation Re est

généralement remplacée par une source de courant (montage miroir).

Pour

augmenter le gain et fmax, les deux résistances de collecteur Rc

sont généralement remplacées par un miroir de courant.

Avec ces deux

modifications, V+ et V- peuvent alors couvrir la plage de tension

allant presque de -Vcc à +Vcc.

Pour

augmenter l'impédance d'entrée qui est généralement faible avec ce

montage, les transistors Q1 et Q2 sont souvent remplacés par des

Darlingtons, des FET ou des MOS.

Finalement,

divers réglages peuvent être ajoutés pour contrecarrer les petites

différences entre les transistors (réglage d'offset ou de bias),

ou encore ajouter deux résistances de faibles valeurs (de l'ordre

de Ze) en série avec chaque émetteur.

Auteur : Marc PHILIPPOT -

Version du 27/05/2020